Coprocessor, a chip used to mitigate specific processing tasks of a system microprocessor.

Coprocessor, a processor that is developed and applied to assist the central processor in performing its inefficient or inefficient processing. There are many tasks that the central processor cannot perform, such as signal transmission between devices, management of access devices, etc., and graphics processing, audio processing, etc., with low execution efficiency and low performance. In order to carry out these processes, various auxiliary processors were born. It should be noted that since the integer operator and the floating-point arithmetic unit are already integrated in the current computer, the floating-point processor is not considered as the auxiliary processor. The coprocessor built into the CPU is also not a secondary processor unless it is independent.

Specific processing task

For example, a math coprocessor can control digital processing; a graphics coprocessor can handle video rendering. For example, the intel penTIum microprocessor includes a built-in math coprocessor.

Kernel connection

The coprocessor can be attached to the ARM processor. A coprocessor extends kernel processing by extending the instruction set or by providing configuration registers. One or more coprocessors can be connected to the ARM core through a coprocessor interface [1].

The coprocessor can be accessed through a special set of ARM instructions that provide a load-store type interface. For example, coprocessor 15 (CP15), the ARM processor uses the registers of coprocessor 15 to control cache, TCM, and memory management.

Extended instruction set

Coprocessors can also extend the instruction set by providing a specific set of new instructions. For example, there is a set of specialized instructions that can be added to a standard ARM instruction set to handle vector floating point (VFP) operations.

These new instructions are processed during the decoding phase of the ARM pipeline. If it is found to be a coprocessor instruction during the decoding phase, it is sent to the corresponding coprocessor. If the coprocessor does not exist or does not recognize the instruction, the ARM considers that an undefined instruction exception has occurred. This also allows the programmer to use software to simulate the behavior of the coprocessor (using the undefined instruction exception service routine).

Internal structure

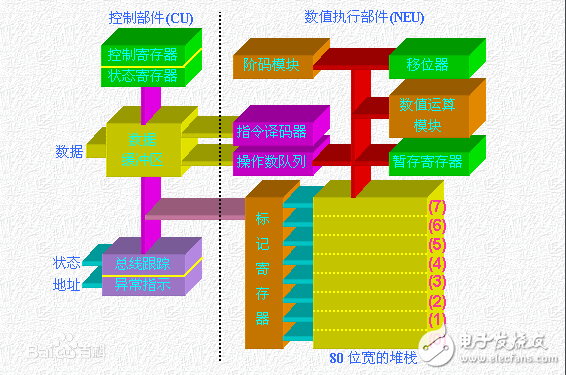

The internal structure of the coprocessor 80x87 is shown in the figure. It can be divided into two main parts: the control unit (CU) and the numerical execution unit (NEU).

The control unit (CU) connects the coprocessor to the system bus of the CPU, and both the coprocessor and the CPU monitor the stream of instructions being executed. If the instruction currently to be executed is a coprocessor instruction (ie: ESCape instruction), then the coprocessor will execute it automatically, otherwise the instruction will be handed to the CPU for execution.

The Numerical Execution Unit (NEU) copies all coprocessor instructions, it has a stack of eight 80-bit registers that store the operands and operations of the math instruction in an extended-precision floating-point data format. result. During the execution of the coprocessor instruction, either the data in the stack register is specified or the push/pull mechanism is used to store or read data from the top of the stack.

In the NEU component, there are also registers that record the working state of the coprocessor, such as status registers, control registers, flag registers, and exception pointer registers. The role of these registers will be described later.

What is the use of the intel coprocessor?Coprocessors have emerged in the field of supercomputers. The Tianhe II, which cooperates with China, continues to occupy the No.1 throne. Intel has recently revealed more technical details of the next-generation product "Knights Landing". The progress is shocking.

The current Xeon Phi is just a coprocessor. It needs to be a PCI-E expansion card. It can be operated with the Xeon E6-2600/v2 series CPU, but it only accelerates.

Fortunately, although Xeon Phi is based on the new IMC core architecture, it is still x86 in essence, so it can also play the role of a central processor, running the operating system natively.

Intel disclosed that Knights Landing will be available in both coprocessor and main processor formats, the latter being installed in a standard server rack, running all programs natively without the need for a dedicated coprocessor. This will greatly simplify the programming difficulty and eliminate the delay of data transfer between memory, PCI-E, and network, thereby improving performance.

The manufacturing process will also progress from 22nm to the latest 14nm, which is more conducive to reducing the core area, expanding the computing scale and reducing the overall power consumption.

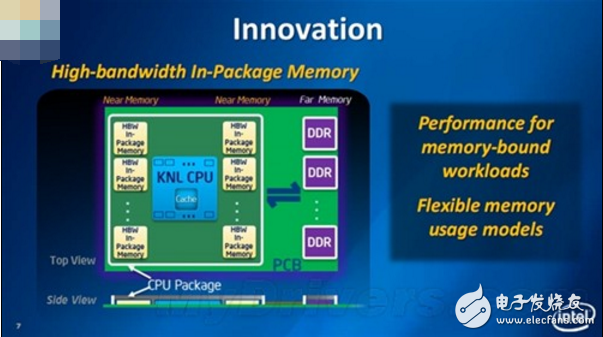

Especially in terms of memory configuration, Knights Landing offers three different ways, and only requires a standard memory programming model, unlike the conceptual design of other billions of ultra-high-performance computing.

Knights Landing's main processor version will internally integrate high-bandwidth memory buffers (glue instead of native), combined with external DDR3 and DDR4 memory, which will greatly improve the performance of memory-intensive applications.

According to a slide leaked earlier this year, Knights Landing will be released in early 2015, supporting the AVX 3.1 instruction set, DDR4 memory, and PCI-E 3.0 bus.

There is no official data for the specific performance. It is said that the double-precision floating-point speed can be increased to about 3TFlops, and the energy efficiency is equivalent to 14-16GFlops/W. Now the Knights Corner has only about 1TFlops and 4-6GFlops/W.

However, this is still a little weaker than the GPU. For example, NVIDIA's Kepler now has 5.7GFlops/W, and the next generation Maxwell can reach 8-16GFlops/W.

1000 Puffs Disposable ecig have a completely enclosed design, reducing the need for charging and replacing cartridges. The no-charge design also reduces the occurrence of faults. It is understood that with rechargeable e-cigarettes, each cartridge needs to be charged at least once and the battery efficiency is extremely low, while the design of disposable ecig can solve this problem very well.

1000 Puff Disposable Vape,Disposable Mini Vape Stick,Puff Disposable Vape,Mini Puff Disposable Vape

Shenzhen E-wisdom Network Technology Co., Ltd. , https://www.healthy-cigarettes.com