There will always be some unexpected behaviors on future nodes, and we are still not very clear about how to deal with them.

For example, it is becoming more and more obvious at the most advanced nodes that quantum effects cause abnormal and unexpected changes in the behavior of electronic devices and signals.

For most chip industries, quantum effects usually occur behind the scenes. Based on data, foundries develop a set of design rules that most companies have never seen before. This explains why foundries and equipment manufacturing companies It is by far the only company directly affected by quantum effects because they have been adjusting their processes and products to minimize these effects. But as the design shrinks to 7/5nm or more advanced nodes, quantum effects are becoming an increasingly common and important problem, which will eventually affect everyone working at these nodes.

“Due to scaling and related requirements, once the size of certain devices becomes very small, quantum effects will occur in the device,†said Anda Mocuta, IMEC’s technical solutions and support director. “For example, as a gate dielectric scaling and device As a result of the increase in the internal electric field, the carriers in the inversion layer are no longer located at the silicon dioxide-silicon interface, but somewhere below, thereby increasing the effective dielectric layer thickness. This effect already exists in CMOS technology It has been a quantum effect for some time. Looking to the future, as the size of transistors decreases, more quantum effects are expected to occur, which is necessary to maintain static electricity and reduce gate length."

The quantum effect has been observed, studied and proposed for many years, and it is not only in the semiconductor industry. For example, quantum tunneling has been documented in the study of alpha particle decay for nearly a century. But in the chip world, these quantum effects will appear in a variety of strange behaviors, and these behaviors cause a variety of problems.

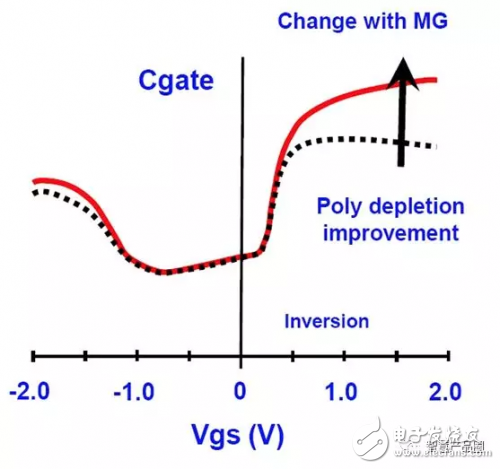

"Quantum effects have always existed," said David Fried, vice president of computing products at Covent's Lam Research division. "Without understanding the periodic lattice and quantum effects, you cannot really solve the transistor equation. The problem is how much it affects your understanding of the physical and electrical behavior of the device. If you go back to 10 to 15 years, we have high k Before the metal gate, we have a polysilicon depletion effect on one side of the gate, and a quantum confinement effect, in which the carrier channel is not located at the interface of the transistor. Due to the step function density in the transistor channel, it will be slightly A little farther. A little farther away from the interface is the quantum effect. At 130/90/65 nm, it becomes a measurable δ of the inversion capacitance behavior. We have conducted research and study, and built it into our device prediction model. However, We all like high-K metal gates. The metal gate eliminates the depletion of polysilicon. We have better field coupling in the channel and have begun to adopt some technical measures to reduce these quantum effects."

Figure 1: Metal gate improvement on polysilicon depletion layer and related capacitance and drive current improvement

In the scope of 7/5nm and more advanced nodes, a new set of worrying data has been added to the list related to quantum effects.

"You can see the increase and change in the roughness of the wire edge, which brings us open or short circuits that we don't want to see," said Gary Patton, GF's chief technology museum. "This means you have to optimize the grounding rules as much as possible to maximize the mass production of EUV."

About memory and its directionFlash memory is the first place where chip manufacturers begin to experience quantum effects. Since a few years ago, NAND storage companies have reported unexpected violations of data movement and outflow in memory.

"This is one of the main reasons flash memory moves to vertical NAND." said G. Dan Hutcheson, CEO of VLSI Research. "The problem is that you won't necessarily get what you want. The system is designed to work in a random world, but when you enter the quantum world, it does not work the way you should think, and there are not enough electrons. What's wrong with the quantity measurement."

There are some ongoing studies trying to minimize the tunneling of electrons through thin layers of material. One such method is called a spin lattice, which can localize or "contain" stray electrons. Spin transfer torque (STT) MRAM uses electric current instead of magnetism to change the spin of electrons.

"The problem with the tunnel for many years was that it was too slow and too difficult to implement," Hutcheson said. "The other direction of quantum effect research is how to make the material consistent enough so that these problems will not arise. This is also what some large equipment companies have been focusing on."

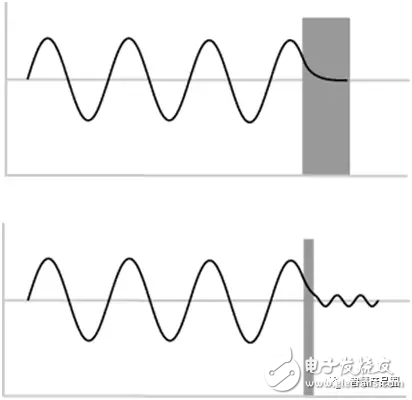

Figure 2: Schematic diagram of electron wave function of ultra-thin barrier tunneling

Gate tunneling is a key reason for introducing high dielectric constant gate materials. For the desired equivalent oxide thickness, their increased physical thickness reduces tunneling. But it is not possible at advanced nodes, because the gate oxide will scale with other feature sizes.

8-port USB charger is portable

8 port USB charger contains a 120W high -power charger that can be charged quickly. At the same time, this 8 -port USB charger built -in independent IC chip can ensure that your device is automatically generated after connecting the best current; The charger is portable, the mini version of the USB charger, when you go out to travel, put it in a trunk or backpack, you will not take up a lot of space. Petite and lightweight saving a lot of space for you. No matter where you go, it will not affect you. Traveling is actual available.

8Port Usb Charger,Usb Charger,8-Port Usb Charger,Power Adapter Wall Quick Charge

shenzhen ns-idae technology co.,ltd , https://www.szbestchargers.com