The economy of the SoC era is driving innovation in verification. A key feature of innovation is the "S" (system) in the SoC (system on a chip). Although the chip has become more complex, the key drivers of "complexity" to describe this verification innovation are not sufficient and accurate. Today, chip verification has become a system-level verification and validation, which has a variety of impacts.

More and larger system designs and the growing importance of embedded software mean more companies need hardware simulation, and more design teams need to step in from the module level to the system level. They need a holistic software simulation to the hardware simulation process to bring the hard work they have done at the module level to the subsystem and system level and reuse. This saves a lot of time and improves the quality and productivity of the verification. For example, you don't have to write a new test platform every time you combine more modules and subsystems.

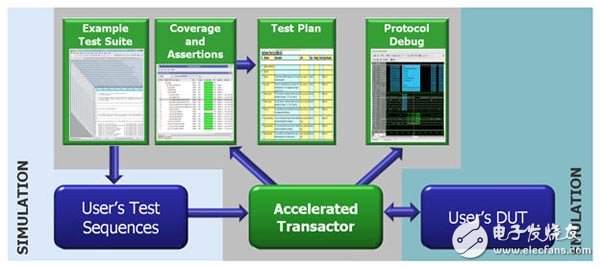

To achieve this overall process, it is critical to establish a very high-speed serial connection between the host workstation and the hardware accelerator (called the co-model co-modeling channel) to transport packets. In collaborative modeling, a reusable test platform created on a workstation for advanced software simulation verification is connected to the hardware emulator via a transactor transaction processor, which is placed on the hardware accelerator together with the DUT. These accelerated transaction processors convert high-level transactions into signal-level stimuli to drive the DUT, enabling the hardware accelerator to perform verification at 10,000 times the speed of the software simulator. The collaborative modeling channel performance required to increase these speeds depends on fast physical links and highly optimized software layers; so far, this only applies to the Veloce platform.

The ability to exchange transactions at this dazzling speed makes the collaborative modeling interface an ideal channel for flexible, multi-layered processes that use the same unified verification method (UVM) test platform for software simulation and hardware acceleration. Verify IP, coverage statistics, assertions, power-aware technology with Universal Power Format (UPF), and debugging tools. All of these technologies can even be run on the same workstation, and hardware accelerators can feed coverage and assertion data back into the same Universal Coverage Database (UCDB).

Figure 1. Establishing an overall software simulation to hardware simulation process through synergy between the simulator and the simulator.

In this way, the usage model of the hardware accelerator can be fundamentally converted. One important benefit is that hardware accelerators can still speed up software emulation, but it does much more than that. It allows users to perform complete chip verification using software and all peripherals, whether they are in-circuit emulation (ICE) hardware peripherals or virtual software peripherals. It also allows a lot of work done in design simulation, including test platform and verification IP, to be transferred to the hardware accelerator.

To take full advantage of hardware simulation investments as a true enterprise verification resource, hardware simulation must undergo a revolution from project-bound engineering lab instruments to data center hosting global resources. The change was first to eliminate the confusing cables, speed adapters, and physical devices in the ICE setup and replace them with virtual appliances. For example, Veloce VirtuaLAB peripherals can be reconfigured immediately to support multiple projects and rapidly changing priorities, as these virtual models of common peripherals such as USB, Ethernet, PCIe, and multimedia are hosted on standard data center computers. Rather than a proprietary hardware target. Virtual peripherals take hardware accelerators out of the lab and into the data center, so they can be used by multiple design teams in multiple locations. In this way, not only can companies use their simulators to do more, but everyone in the entire company can use it all the time.

To enable multiple engineers responsible for different projects to access the company's simulation environment at this level, enterprise server software needs to effectively manage global simulation resources and integrate these resources into a commercial queue manager to become a high-volume entity. Enterprise servers need to determine the most efficient place to run each job and immediately support high-priority work by suspending lower-priority work.

With this holistic software simulation and hardware simulation process, designers can achieve full functional verification by adding minimal effort, as all of these technologies have been integrated across software simulation and hardware simulation platforms. Users can largely believe that they can get their SoC into the filming phase with minimal effort. Similarly, they can achieve coverage in less time and have a better chance to achieve their verification goals on schedule.

This series is a professional advertising LED Screen for classic indoor use. Small in size, it is convenient to be placed in shops, cafes, clothing stores, restaurants and many other places. Easy to operate. Wifi connect and controlled by mobile App, USB to play video or display pictures. Cabinet with wheels, easy moveable. Regular size around 640*1920mm in Poster LED Display, it will be a very good choice for advertising screen for all shops. It can be customized to ourdoot types or different sizes.

Waterproof Led Display Screen Wall,Led Display Advertising,Led Display Advertising Billboards,Full Color Led Display

Guangzhou Cheng Wen Photoelectric Technology Co., Ltd. , https://www.leddisplaycw.com