Many high performance instruments use dynamic random access memory (DRAM) as the local memory, which is a high density, high bandwidth memory. By choosing an NI FlexRIO FPGA module with DRAM, you are free to incorporate such local storage into your application. Typical DRAMs range from simple local storage for record-based acquisition/generation to long delay chains for channel simulation applications. This article explores the implementation of DRAM in NI FlexRIO and learns how to use powerful DRAM abstractions and interfaces in the NI LabVIEW FPGA Module.

Use DRAM

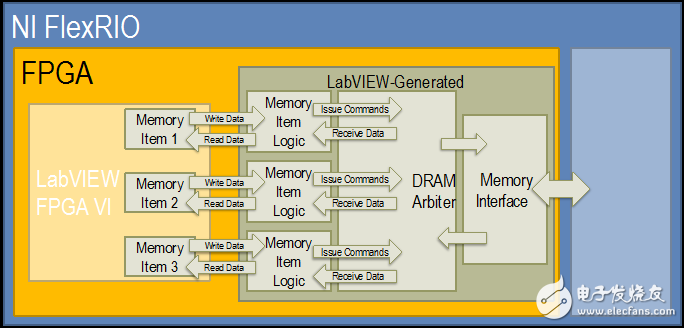

The local LabVIEW FPGA interface connects DRAM through memory. This interface simplifies the underlying complexity of physical DRAM communication on the module, competing request arbitration for DRAM resources, and memory segmentation (to maximize usage flexibility). Therefore, this interface helps users easily read and write DRAM.

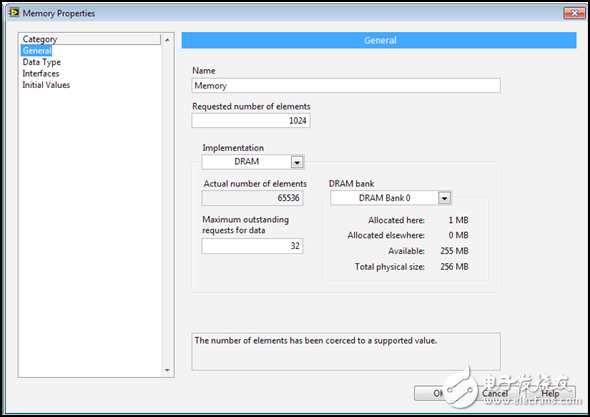

DRAM memory items can be created in the same way as block memory or lookup tables in the global project view. To create a DRAM memory item, right-click on the target for which you want to create a new memory item and select New»Memory. Then select "DRAM". Each memory item corresponds to a DRAM bank. If no other memory item is allocated to the selected DRAM bank, the memory item can cover the entire bank.

With memory items, you can split a complete DRAM space into multiple small blocks of memory so that each small block of memory can be accessed independently through different parts of the LabVIEW FPGA code. LabVIEW creates an arbitration code that allows all corresponding interfaces to access DRAM equally. The following figure is the logic generated by LabVIEW that provides access to specific DRAM banks.

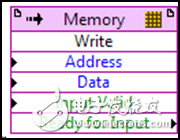

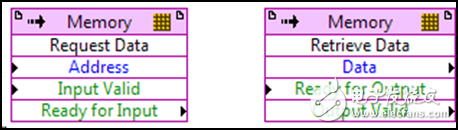

2. Write method The write method in the figure below is very straightforward. When writing, you need to specify an address to enter data. When the input to Input Valid is true, the write command will enter the interface. The Ready for Input port indicates if the interface is ready. If the value of the port is false, the data will be ignored. To avoid loss of information, data can only be added to the write method when the value of Ready for Input is guaranteed to be true.

3. Read Method The memory read interface uses two methods: requesting data and retrieving data. The first method—request data first receives the address of the target data and then requests the data at that address through the memory controller. But keep in mind that there will be a long delay after DRAM accepts arbitration and non-deterministic events (such as DRAM refresh) requests. Therefore, the data is not immediately available. Instead, all requests are queued and processed according to the order in which they were received. After a certain amount of time, the retrieve data method displays the data to be requested next and determines the output value of Output Valid to indicate whether the data is available. The data is only displayed when the value of the Ready for Output port is set to true. The message passed to the memory interface is that the logic that will use the data is ready to receive data.

4. Other resources

Learn the three steps to efficiently use DRAM in NI FlexRIO to optimize DRAM access for NI FlexRIO

Learn more about NI FlexRIO

Learn about NI RF and wireless test products and solutions

Learn about NI automated test platform resources

Our Enclosures have the solution for products in industrial environments with high demands on safety, durability, reliability and cost saving for the end user. Designed for use as instrument enclosures, electric, hydraulic or pneumatic control housings, electrical junction boxes or terminal wiring enclosures. Provides protection where equipment may be hosed down or otherwise be very wet, or indoor outdoor applications for full weather protection.

Outdoor Rack Enclosures,Fiber Optical Joint Enclosure,Industrial Enclosures,Cables Distribution Enclosure,Fiber Splice Enclosure,Wall Mount Enclosure

Sijee Optical Communication Technology Co.,Ltd , https://www.sijee-optical.com